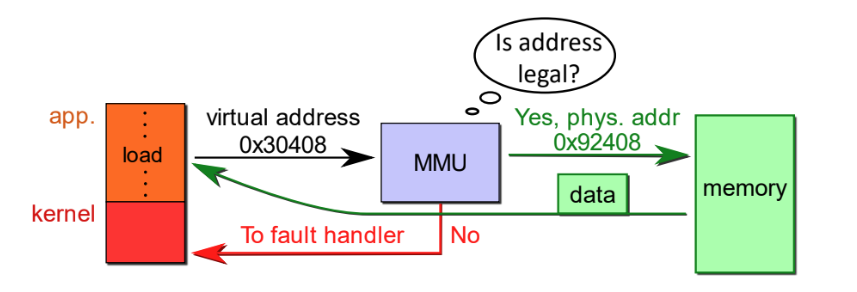

Memory Management Unit

- Maps virtual address to physical address

- Enforces protection

- Prevents one app from messing with another app’s memory

- Allows programs to see more memory than exists

- Maps some memory accesses to Secondary storage

Software Managed

- Simpler hardware which asks software to reload pages

- Requires fast exception handling and optimized software

- Enables more flexibility in the TLB

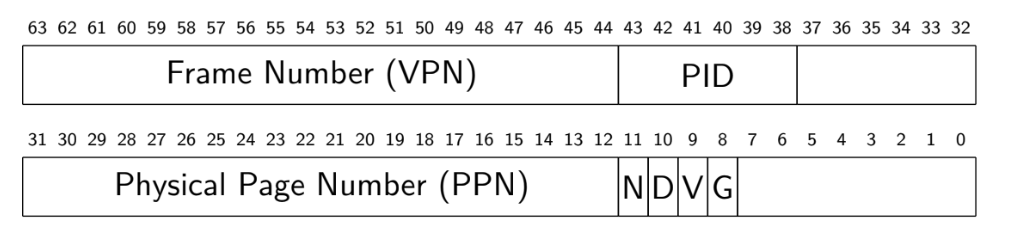

MIPS MMU

- Hardware has 64-entry TLB

- TLB Entries: 64-bit

- PID: Process ID

- Allows multiple processes to use TLB

- N: No Cache

- D: Writeable

- V: Valid

- G: Global

- Pages shared across all address spaces

- PID: Process ID

MIPS TLB Instructions

tlbwr: TLB write a random slottblwi: TLB write a specific slottlbr: TLB read a specific slottlbp: Look for the entry that matchesc0_entryhi

Need to load information into registersc0_entryhi: high bits of TLB entryc0_entrylo: low bits of TLB entryc0_index: TLB Index

Exceptions

UTLB Miss

- user segment page number not found in TLB

TLB Miss - kernel segment page number not found in TLB

TLB Mod - Generated when writing to read-only page

UTLB handler is separate from general exception handler

- UTLBs are very frequent and require a hand optimized path

Hardware lookup algorithm

- If the most significant bit is 1 and in user mode → address error exception

- virtual address ≥ 0x8000 0000 (kernel memory)

- If no VPN match → TLB/UTLB miss exception

- If PID mismatch and global bit not set → TLB/UTLB miss

- If valid bit not set → TLB/UTLB miss

- Write to read-only page → TLB mod exception

- If N b it is set → directly access device memory

Hardware Managed

- Hardware reloads TLB with pages from a page table

- Typically hardware page tables are Radix Trees

- Requires complex hardware

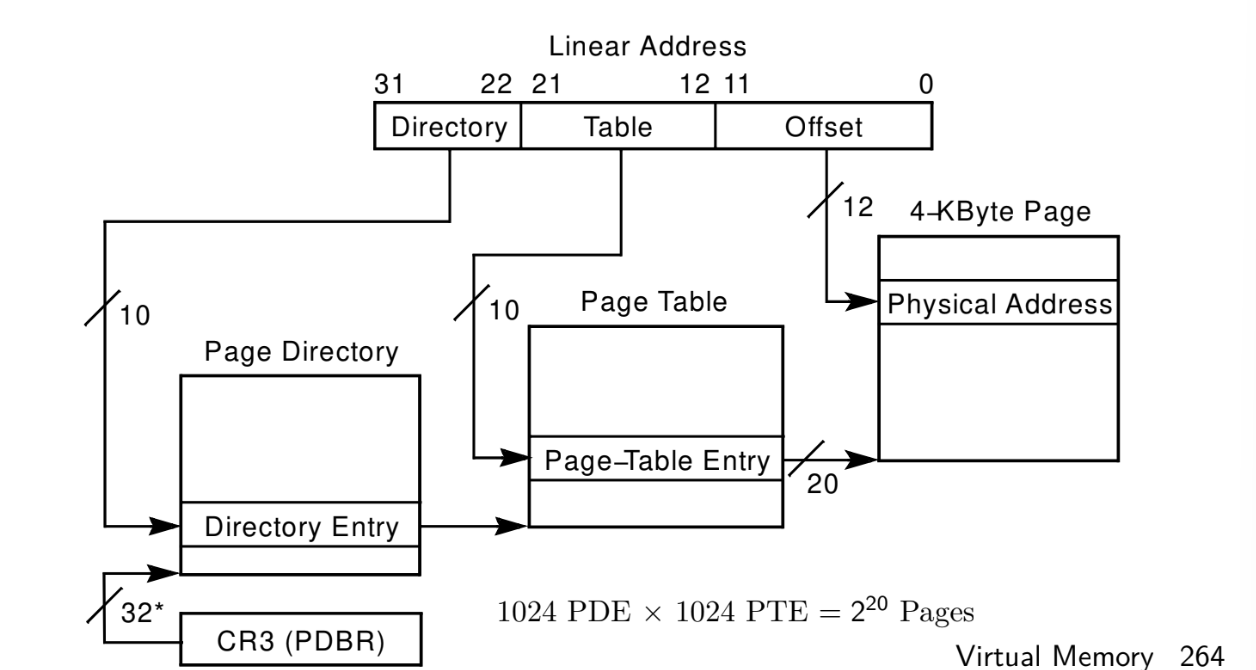

x86

TLB managed by Hardware and Microcode

- Two levels of TLBs each acting as a cache

- TLB automatically reloaded from page table by processor

OS builds Radix tree describing memory layout

Contains much of the same information as MIPS - Global page

- all processes can access it

- Accessed

- whether the page has been accessed recently

- Cache disabled

- do not store in cache

- Write-through

- enable write-through

- User/Supervisor

- privilege needed to access page

- Read/Write

- is the page writeable

- Present

- in RAM rather than is swap space on the SSD

Directories ignore the global page bit

Specifies page size instead of Page Table Attribute

- in RAM rather than is swap space on the SSD

x86 Paging

Normally 4KB pages

- Page directory

- 1024 PDEs (page directory entries)

- Each contains physical address of a page table

- Page table

- 1024 PTEs (page table entries)

- Each contains physical address of virtual 4K pages